SEGA MARK III

SEGA MARK III SEGA MARK III

SEGA MARK III  |

||||||||||||||||

|

|

||

|

||

|

||

|

回路やアクセス方法についてはEnriさんのサイトを参考にさせていただいた。記事によるとOPLLのIOポートは#F0-F1h。デバイスイネーブラが#F2hのbit0に存在し、ソフトウエアではこのレジスタを読み書きすることでFMサウンドユニットの存在を確認するらしい。 MK3本体ではIOデコード信号/KBSEL信号をVDPが出力しているが、A7,A6しか見ていないので#C0-FFhのIOアドレスは区別されず、OPLLのポート#F0-F1hはキーボードやジョイパッドのポート#DC-DDhと同一とみなされる。このためFMサウンドユニット内の回路では、#C0-FFhアクセス時にA1,A2を読んでIOアドレス区分を拡張し、11xxx00xbへの書き込みでOPLLアクセス、11xxx01xbの読み書きでF2レジスタアクセスとみなしている。更に、IO競合を避けるため、11xxx0xxbの読み込み時は/JOYSEL(本体側でプルダウンされている)を立ち上げ、ジョイパッドのデータ出力を禁止している。 なお、前述のピットポットで動作不良が生じる件についてはEnriさんの記事に詳細が書かれている。以下に引用する。

#F2hレジスタの誤読が原因のようなので、#F2hレジスタを無効化する仕組みがあれば不具合を回避でき、同時にFMサウンドユニットの存在を隠すことができるのでOPLL対応ソフトをDCSGサウンドでプレイすることもできるはずだ。 |

Wikipediaによると、MK3とFMサウンドユニットの組み合わせにおいて、「本体の音源をFM音源と一緒に鳴らすとノイズが入る」とされている(2021年8月現在)。この件について検証してみたい。

実際に純正FMサウンドユニットをMK3に接続し、OPLL+DCSG同時発音させたらどのように聞こえるのか、MasterSystem IPLのスペースハリアーBGMで検証したところ、OPLLサウンドは聞こえるがDCSGサウンドがほぼ聞こえない状態になった。ノイズが入るというよりも、音量バランスが極端にOPLL側に偏っているために事実上DCSGがミュートされてしまう、というのが真相のようだ。

どうもDCSGは無音時にノイズを撒き散らす厄介な性質があるようだ。原則としてMK3のゲームソフトではOPLLとDCSGのどちらかしか使わないことになっているので、OPLL使用時はDCSGを切り離してしまったほうがいい。FMサウンドユニットでは敢えてOPLLとDCSGの出力インピーダンスを合わせずに結合することで、DCSGのミュート回路を省略したのかも知れない。 ところで、国内版MasterSystemでは例外的なDCSG+OPLLの同時発音によるスペースハリアーのBGMを聞くことができるが、このことはMasterSystemに適切なミキシング回路が入っていることを示している。しかし、不思議なことにOPLL対応ゲームを動作させてもDCSG由来のノイズが混入していない。ひょっとしたらMasterSystemではDCSGもミュート制御しているのでは?と考えていたところ、Enriさんの記事に気になる情報があったことを思い出した。以下に引用する。

IOポート#F2hのレジスタであるが、bit0はOPLLのイネーブラであることが明らかとなっている。気になったのはbit1で、MasterSystemのデモではbit1=1を書き込んでいるとのことで、実際にROMを読んでみたところ、00A6h~で#F2hに03hを書き込んでいることが確認できた。OPLL対応ゲームの初期化プログラムも何本か読んでみたが、一様に#F2hには01hを書き込んでおり、IPLデモだけ例外的に03hを書き込んでいるようだ。これは怪しいとMasterSystem実機でIPL ROMの00A6hの03hを01hにパッチしてBGMを聞いてみたところ、OPLLサウンドだけが鳴り、DCSGは聞こえなくなった。つまり、bit1=0操作によりDCSGはミュートされたのである。 検証結果に基づいてEnriさんの表を埋めると以下のようになる。OPLL増設基板でもこのレジスタを実装する必要があるだろう。

MasterSystem実機のDCSG音声回路を追ってみたところ、ミュート制御はカスタムIC(315-5297)で行っているようである。改めてネットを調べてみると、国内版MasterSystemの調査記事が海外にあった。音声ミュート回路についても言及されており、ほぼ既知のレジスタだったっぽい。無駄に遠回りした気がするが、検証の過程は面白かったのでヨシとしよう。 |

画像クリックで拡大 |

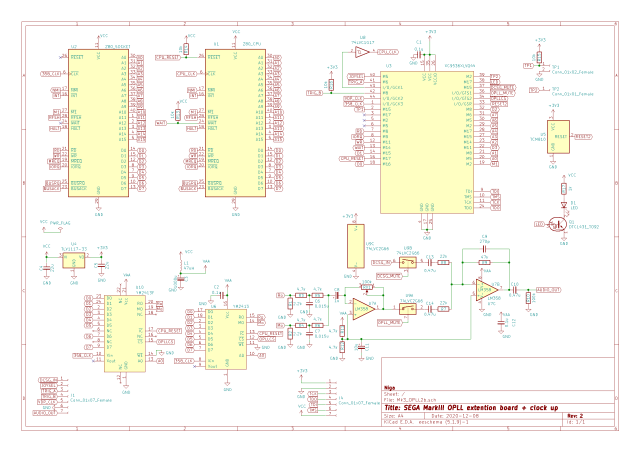

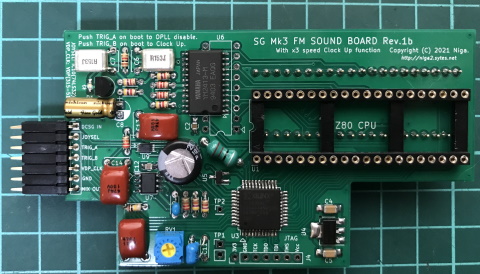

| 以上の知見を踏まえて回路を設計してみた。OPLL増設の手法につては、A1Fのメモリ増設基板同様のCPU下駄方式で、音声出力の積分回路はMSX MUSICと同等にした。 OPAMPは1段目でOPLL音声の0~20倍の反転増幅、2段目でOPLLとDCSGのミキシング回路を構成した。ミュートは2chのアナログスイッチ(74LVC2G66)とCPLDのレジスタで制御する。 #F2レジスタは起動時のジョイパッドのトリガーボタンの状態を見て切り離せるようにした。デフォルトは#F2レジスタ有効とし、1ボタンを押下しながら電源投入にて無効にする。これで任意に「FMサウンドユニット」としての機能を切り離すことができる。 |

|

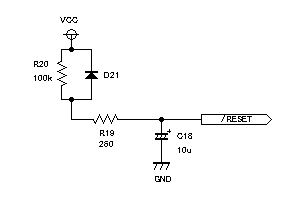

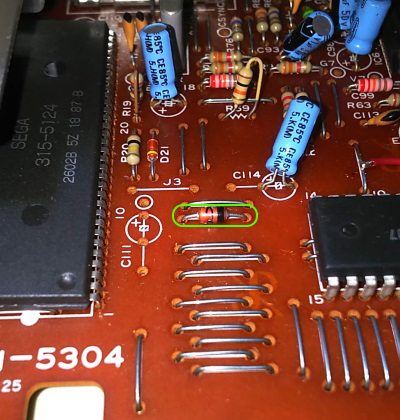

少し横道にそれるが、MK3のメインボードで生成されているリセット信号は左回路図のような簡易的なものである。電源投入時はR20を介してC18を蓄電することで/RESETの立ち上がりを遅延させ、電源断時はD21を介して素早く放電し/RESETを立ち下げるという仕組み。 これらがCPUとVDPに与えられているが、どうもCPUがVDPより早く起動するとゲームソフトが起動しない不具合が発生する模様。 |

|

MK3には、左画像の位置にダイオードが実装されている個体が存在する。通常はジャンパー線でショートされているが、部品面からジャンパー線を切ってダイオードを後付けした個体もあるそうだ。おそらくメーカーによって行われた改修だろう。 ここはVcc電源ラインを中継するポイントであるが、調べてみるとダイオードの手前にはVDP、VRAM、ビデオエンコーダ、RFコンバータ、前面拡張端子はレギュレータがあり、これらは+5Vに直結されていた。そしてダイオードを経由してCPU、RAM、ジョイパッド、カートリッジ・カードスロット、DINコネクタの電源ラインが繋がっている。 ダイオードを経由したVcc電圧は0.8V程度低下する(順方向電圧降下)。定格5VのCPUを4.2Vで駆動するのも問題だが、VDPとCPUのバス電圧が違うのはマズくないか。 何故わざわざこんなダイオードを後付け改修したか考えてみたが、CPU電圧を下げることにより、VDPが起動する前にCPUが立ち上がらないようにする意図があったのではなかろうか。MasterSystemではシステム起動時にIPL ROMのプログラムで約2秒CPU の動きを止めており(Enriさんのサイトに情報あり)、MK3においてCPUの立ち上がりを遅くする必要性は認識されていたと推定できる。 |

|

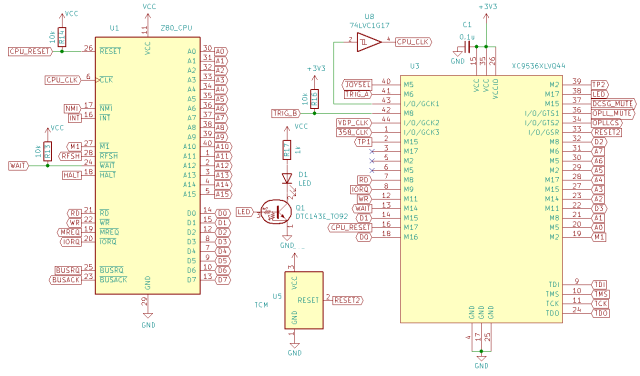

| 以上の問題点を解消するために、OPLL増設基板ではリセット回路の改修も同時に行うこととした。まずCPUの/RESET端子をMK3本体から切り離す。そして3.3Vのリセット信号をリセットIC(TCM809R)で生成、CPLDのリセット入力(GSR)に接続し、CPLD内部で遅延してCPUの/RESET端子にオープンドレイン出力とした。これでCPUの起動は遅延され、件の定格無視なダイオードは撤去可能と思われる。 音源制御とリセット信号の遅延回路をXC9536XLに入れても、IOピンやマクロセルには余裕がある。開発協力者のtakedaさんからクロックアップ機能の提案があり、せっかくなのでCPLDに入れてみることにした。クロック原発はVDPとCPUパターンから10.74MHzと3.58MHzを取得。これをCPLDで切り替えてCPUクロックに出力するが、CPLDからはHレベル3.3Vしか出力できないため、CPUのクロック信号の定格(H>Vcc-0.6V)を満たせない。オープンドレインに出力にすると波形が鈍ってしまうのでシュミットトリガのバッファIC(74LVC1G17)を噛ましてレベル変換した。どちらのクロックで動作させるかは、起動時のコントローラのトリガ2の状態を読み取って決定すれば良いだろう。状態確認のためのLED出力も用意した。 FS-A1WXシリーズで実証されているように、3倍速クロックではVDPとOPLLが足を引っ張ると予想される。IOアクセスはCPLD内部でデコードできるので、VDPとOPLLアクセス時に適当なクロック数WAIT信号を発行できるように作っておけば良いだろう。 |

|

諸々試行錯誤の末、3作目で出来上がった基板がコチラ。 OPLLはDIP版のほか、SOP版も実装可能にした。 |

|

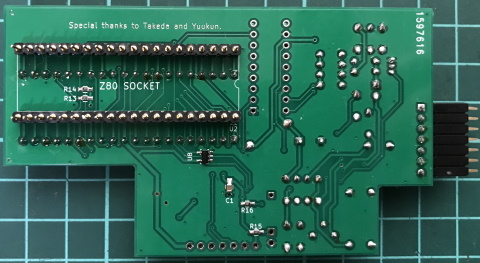

CPUクロックは無駄に引き回すと動作不良の原因になる。クロックバッファは背面に実装。 |

|

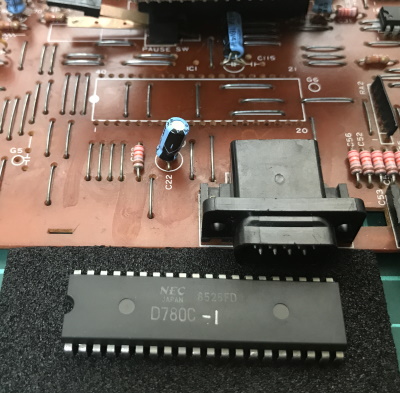

まずは元のCPU(uPD780C-1)を引っこ抜く。片面基板なのでそれほど難しくはないが、パターンを傷めないように丁寧に作業する。ハンダ吸い取り線は使わず、吸い取り機を使うべし。シュッポン吸い取り機で十分。事後に基板を強い光源で透かして断線がないか確認しておくとよい。 CPU跡地に40pのICソケットを実装しておくことで、改造前の状態にも簡単に戻せる。 |

| 基板のジャンパーピンには、MK3のメインボードから7本の信号をワイヤーで引き出して接続する。 |

|

|

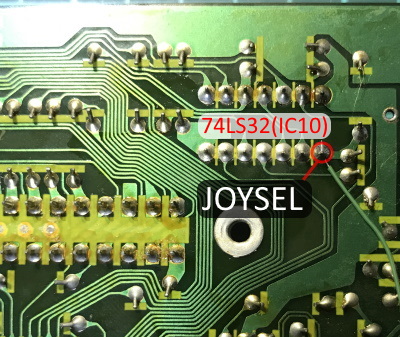

JOYSEL信号はFM音源アクセスとジョイパッドアクセスを区別するために使われる。IC10の74LS32の1pに接続。 |

|

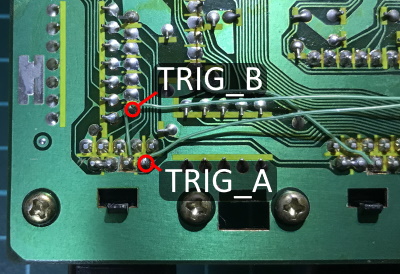

OPLL切り離しスイッチとしてTRIG_Aを1p側コントローラの1ボタンに接続する。通常起動でFM音源は有効、1ボタン押しながらの起動でOPLL無効になる。 クロックアップ機能を使う場合はクロックアップ発動のスイッチとしてTRIG_Bを1p側コントローラの2ボタンに接続する。通常起動でクロックアップ無効、2ボタン押しながら起動でクロック3倍速となる。 |

|

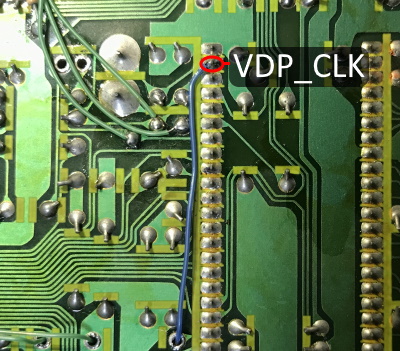

10.74MHzクロック信号 VDP_CLK はVDPの31pから取得する。なるべく短く配線したほうがよい。 |

|

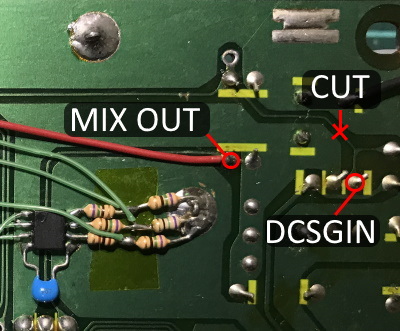

DCSGサウンドの経路をパターンカットで切断し、入力側DCSGINと、出力側MIX OUTを各ポイントに接続する。 GNDは適当に取り出しやすいところに接続。 |

| OPLL増設基板をCPUソケットに装着し、以上の7本のワイヤーをピンヘッダコネクタに接続して、熱収縮チューブで保護した。ワイヤーは適当な未使用のホールを利用してパターン面に誘導するとよい。 |

| 以上で改造は完了。ゲームを起動して音源を鳴らしてみたところ電源ノイズが気になったため、適当に電解コンデンサの空きパターンに部品を追加したところ改善が見られた。USB電源にはやたらノイズの多いものがあるが、当サイトでは林檎のマークの純正品を推奨する。元々MK3は定格はDC9V/850mAなので、iPhone用 1A出力のものでOK。 なお、DCSG音声に混入する映像信号と連動したノイズは、ある程度以上は除去できなかった。DCSGとVDPが同じチップに存在するので致し方なしか。 |

| 3倍速の元ネタはつじかわさん考案のMSX2+ FS-A1WXシリーズのクロックアップ改造である。元々WXシリーズは1.5倍速クロック切り替え機能を持っているが、クロック源を高速化し、VDPとOPLLのアクセス時にwaitを発行することにより3倍速を実現している。関連記事はコチラ。 この回路では、VDP読み書き時のCSの立下りで7.2us、OPLLアクセスのA0=0時のCSの立ち上がりで7.2us、A0=1時のCSの立ち上がりで16usのWAITを発行している。OPLLを付けたMK3も似た構成になっているので、同様のタイミングでWAITを与えてやれば3倍速で動作する可能性は高そうである。 今回の基板ではCPLDに同等のWAIT回路を実装することになるが、実際の作業はVHDLにIOデコーダとカウンタやスイッチを記述するだけなのでラクなものである。ゆうくんさんの協力のもと、適当なWAITのクロック数を探ってみたところ、VDPアクセス時のwaitは70clk(6.5us)あたりがボーダーラインのようである。M1サイクルに1wait必要であることも判明し、これらをVHDLに反映した。 |

|

当然ながら3倍速クロックアップに切り替える場合、CPUは高クロック版が必要になる。 実験として、手持ちのZ80互換CPUで試してみた。上からZilog Z0840004PSCとROHM BU18400A-PSがMSX2から取り外したもの。NEC upD780C-1がMK3から外したもの。これらは3.58MHz品で、3倍速クロックでは動作しなかった。 下から2番めのTOSHIBA TMPZ84C00AP-8はヤフオクで入手したもの。8MHz品であるが、この個体は10.74MHzでも問題なく動作した。 一番下のZilog Z84C0010PEGはMOUSERで購入したもの。10MHz品で10.74MHzでも問題なく動作した。Zilog純正品は2021年現在も現行商品で、今でもDIP版の新品が手に入るのでオススメ。Digikeyやマルツ経由でも入手可。 |

|

|

| ほとんどのゲームではVDPクロックでタイミングを測っていると思われ、CPUクロックだけ速くしてもあまり変化が見られないが、処理落ちが激しいゲーム(ALESTE)ではハッキリと違いが現れた。CPUの思考が入るゲームでも差がでそうだが、手持ちがないので不明。まぁ、オマケ機能なので過度な期待はしないほうがよいかと。 |

|

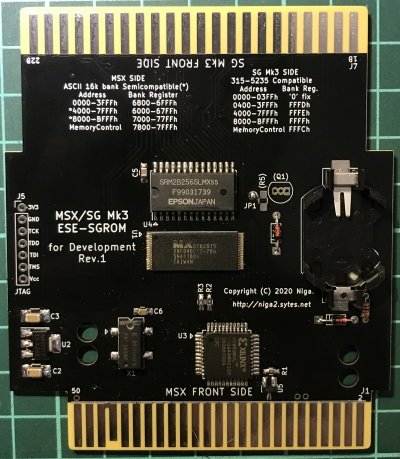

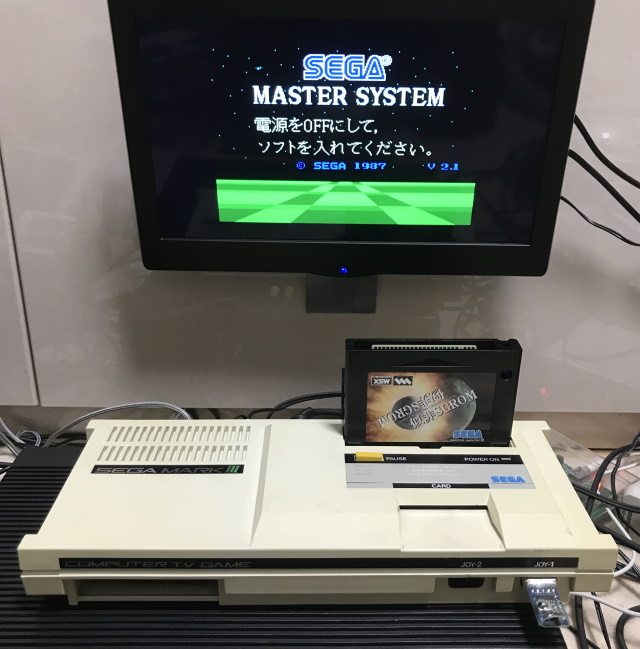

せっかくMK3をMSXっぽく改造できたので、MK3用の似非ROMっぽいものを作ってみた。名付けて「似非SGROM」。 MSX、MK3両刀遣いの変態カートリッジで、MK3に挿すとセガマッパ互換、バックアップSRAM付きの4Mbit FlashROMカートリッジとして機能する。 MSXに挿すとASCII 16kバンク準拠の似非ROMカートリッジとしてFlashROMにアクセス可能で、書き換えはMSX-DOS上のアプリで行う。 MSXのMegaROMゲームを動作させることもできるがASCII 16kバンク限定で、バンクレジスタの初期値や、リセット時の挙動が異なるので工夫が必要。 |

|

ゲームROMから吸い出したデータをMSXで似非SGROMに書き込んで起動してみた。 CPLDによるMegaROMコントローラはセガマッパとしてフルスペックの315-5235互換。過去に流通していたセガマッパのゲームならほぼ再現できるはず。SRAMは最大容量の32kB搭載しており、データのセーブ・ロードもOK。 なお、オリジナルのROMカートリッジには3倍速クロックアップで起動できないものがあり、おそらくROMが追従できないものと思われる。ROMデータを似非SGROMに書き写すと動くものは動くが、全てのソフトでの動作は保証できない。 |

|

| 適当にケースに入れてMK3に挿すとこのような状態になった。ひっくり返ったMSXカートリッジが違和感ありまくりである。ちなみに基板サイズをMK3に合わせて作ったら、MasterSystemはスロットが深くて挿さらなかった(笑)。ということで、似非SGROMはMK3専用 MasterSystemには非対応である。 似非SGROMを利用することで、MK3でもMasterSystemのスペースハリアーBGMを流すことができるので、今回の実機解析では大いに役立った。このデモをMK3で起動する場合はROMパッチが必要である。国内版 V2.1の場合は 0125hの "C2h" を "00h" に書き換えればOK。また、 00A7hの "03h" を "01h" に書き換えるとOPLLのみ、"02h" に書き換えるとDCSGのみのBGMが聴ける。 |

改造キット頒布します

キット内容一式

せっかく作ったので、いつものように家電のKENちゃんさんを通して頒布することにした。

無改造状態からのクイック改造マニュアルはコチラ。高速版Z80は付属しないのでクロックアップを試したい方は各自入手のこと。

OPLLの入手性の問題があり、あまり数は用意できないが、興味のある方は担当HRDさんのツイートに注目してほしい。似非SGROMも製品化準備中。

お約束ですが、この記事を見て修理・改造などを行い故障やその他問題が発生しても当方は責任を負いません。各自の責任において情報を広く集めて行うことをおすすめします。

この記事の内容は個人の憶測や見解の誤りを含んでいる可能性があります。内容についてメーカー各社に問い合わせるのは止めましょう。

改造・解析、および試作品の動作検証にご協力いただいたtakedaさん、ゆうくんさんありがとうございました。Enriさんいつも記事を参考にさせていただいています。海外のSMS POWER!の方々の投稿記事も参考にさせていただきました。ありがとうござました。

copyright (C) 2021 Niga.